ELSEVIER

Contents lists available at ScienceDirect

## **Applied Surface Science**

journal homepage: www.elsevier.com/locate/apsusc

# Improved light output power of LEDs with embedded air voids structure and SiO<sub>2</sub> current blocking layer

Shengjun Zhou a,b,\*, Shu Yuan c, Sheng Liu a, Han Ding b

- <sup>a</sup> School of Power and Mechanical Engineering, Wuhan University, Wuhan 430072, China

- <sup>b</sup> School of Mechanical Engineering, Shanghai Jiao Tong University, Shanghai 200240, China

- <sup>c</sup> Quantum Wafer Inc., Foshan 528251, China

#### ARTICLE INFO

Article history: Received 29 November 2013 Received in revised form 24 February 2014 Accepted 5 March 2014 Available online 15 March 2014

Keywords: LEDs Laser scribing Air voids structure Current blocking layer

#### ABSTRACT

GaN-based light-emitting diodes (LEDs) with an embedded air voids structure and a SiO $_2$  current blocking layer (CBL) was fabricated and investigated. The air voids structure was formed between cone-shaped patterned sapphire substrate and GaN epitaxial layer by combining laser scribing with  $\rm H_3PO_4$ -based hot chemical etching. The air voids embedded high power LED showed 8.9% higher light output power due to a strong light reflection and redirection at the interface between GaN and air voids, which could increase the top light extraction of the high power LED. Compared to the air voids embedded high power LED, the light output power of the high power LED by integrating air voids structure with SiO $_2$  CBL was 9.1% higher than that of the air voids embedded LED without SiO $_2$  CBL. It was also found that the simulation results agree well with the experimental results.

© 2014 Elsevier B.V. All rights reserved.

#### 1. Introduction

Light-emitting diodes (LEDs) have advantages of long lifetime, low energy consumption, and compactness with respect to other electric light sources such as incandescent lamps. Due to its numerous advantages, LEDs have been widely used in full-color displays, traffic signals, backlights for cell phone and also has considerable potential in general lighting applications. However, LEDs suffer from problem with insufficient external quantum efficiency (EQE). Generally, the EQE of LEDs depends on both the internal quantum efficiency (IQE) and the light extraction efficiency (LEE). The IQE of LED is limited by high dislocation density, strong piezoelectric filed in quantum wells, and low hole concentration of p-GaN layer. The LEE is limited by the total internal reflection occurring along the GaN/air and sapphire/air interface because the refractive indexes of GaN and sapphire substrate are much higher that of air, which would result in a critical angle for the light escape cone according to Snell's law. The light outside the escape cone is therefore trapped in the LED epitaxial layer and can be reabsorbed by the active layers and metal electrodes, resulting in a decrease in light output power of LEDs.

Due to the total internal reflection, only approximately 4% of the internal light can be extracted from the surface of the conventional

GaN-based LED to the air. Numerous methods have been applied for improving the LEE of the LED, such as textured surfaces [1], surface microstructure [2], photonic crystal [3], patterned indium tin oxide (ITO) [4], current blocking layer [5], graded-refractive-index antireflection coatings [6], patterned sapphire substrate (PSS) [7], and bottom reflectors [8]. In particular, it was well known that PSS technology can improve not only the LEE due to the angled facets that redirected light into the escape cone but also the IQE by the reduction of dislocation density. It is also possible to enhance LEE of LEDs by forming air voids at GaN/PSS interface by chemical etching [9,10]. The current crowding around the p-electrode pad can be effectively alleviated by using the current blocking layer, which can improve both electrical and optical performance of LED.

To achieve higher light output power, the electrical power and the size of LED chip must be increased. Accordingly, high power LED chip is a development goal for general lighting. However, most of the above-mentioned methods have been successfully applied to small size of LED chip with low input power, and few studies focused on the high power LED. In this paper, both air voids structure and current blocking layer was employed to improve the LEE of high power LED chip. In this design, an inverted cone shaped air voids structure was embedded between a patterned sapphire substrate and a GaN buffer layer by combining laser scribing with H<sub>3</sub>PO<sub>4</sub>-based hot chemical etching process to improve the top LEE of the high power LED, and a SiO<sub>2</sub> CBL inserted beneath the p-electrode pad was utilized to improve current spreading performance of the high power LED. Optical simulations of the

<sup>\*</sup> Corresponding author. Tel.: +86 15827348861. E-mail addresses: steveroke@163.com, 40986782@qq.com (S. Zhou).

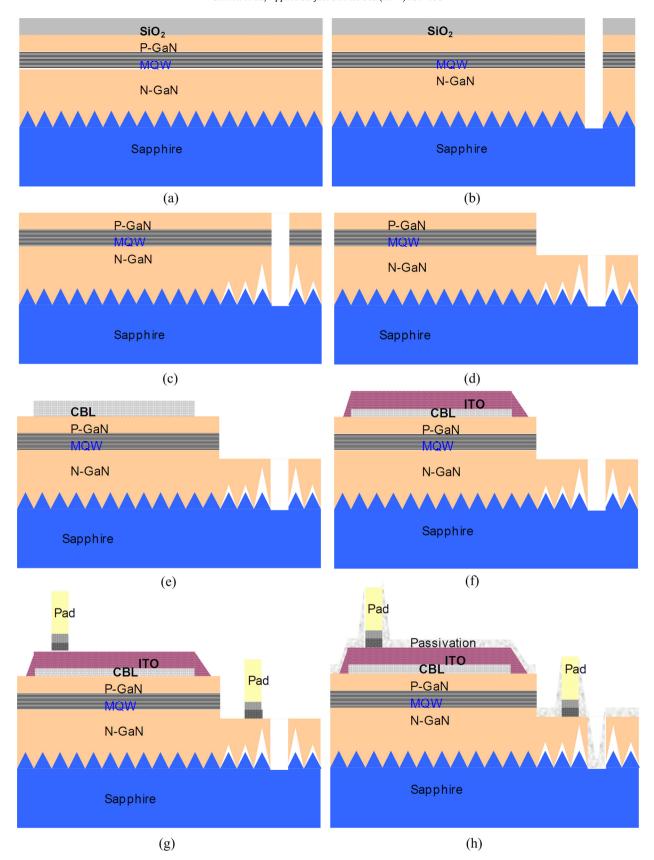

Fig. 1. Fabrication process of the high power LED with embedded air voids structure and SiO<sub>2</sub> CBL.

voids embedded LEDs were also performed and compared with the experimental results.

#### 2. Experiments

LED epitaxial layer was grown on the PSS by metal organic chemical vapor deposition (MOCVD) system. Trimethylgallium (TMGa), trimethylindium (TMIn), and ammonia (NH $_3$ ) were used as precursors. Silane (SiH $_4$ ) and biscyclopentadienymagnesium (Cp $_2$ Mg) were used as the n-dopant and p-dopant source. The LED epitaxial layer consists of a 30-nm-thick GaN nucleation layer, a 1.5- $\mu$ m-thick undoped GaN buffer layer, a 3- $\mu$ m-thick Si-doped n-GaN layer, a lnGaN/GaN multiple quantum well (MQW), a 100-nm-thick Mg doped p-AlGaN electron blocking layer, and a 190-nm-thick Mg-doped p-GaN layer. The lnGaN/GaN MQW structure consists of twelve pairs of 3-nm-thick ln $_0$ 16Ga $_0$ 184N well layers and 12-nm-thick GaN barrier layer. After the epitaxial growth process, the LED wafer was subsequently annealed at 750 °C in N $_2$  atmosphere to active Mg in the p-GaN layer.

The fabrication process flow diagrams of the high power LED by integrating air voids structure with SiO<sub>2</sub> CBL were shown in Fig. 1. The detailed proceeding steps were illustrated in the following:

(a) a 3.0-μm-thick SiO<sub>2</sub> was deposited onto LED wafer to serve as the protection layer during wet etching process; (b) nanosecond laser scribing was then performed to scribe the LED wafer along the designed scribing line. The nanosecond pulse laser has a wavelength of 355 nm, a repetition rate of 50 kHz, and an average output power of 1 W. The depth and width of the laser-scribed trench are 15 µm and 5 µm, respectively; (c) the scribed samples were then wet etched by a mixture of H<sub>3</sub>PO<sub>4</sub> and H<sub>2</sub>SO<sub>4</sub> solution  $(H_3PO_4:H_2SO_4=3:1)$  at 260 °C for 6 min (LED II), or 15 min (LED III), or 20 min (LED IV), respectively, and the SiO<sub>2</sub> protection layer was removed by buffer oxide etch solution after the H<sub>3</sub>PO<sub>4</sub>-based hot chemical etching process; (d) Cl<sub>2</sub>/BCl<sub>3</sub>/Ar inductively coupled plasmas was used to etch the LED samples until the n-GaN layer was exposed, and the etch depth was 1.2 µm; (e) A 182-nm-thick SiO<sub>2</sub> CBL was subsequently deposited on p-GaN surface by plasma enhanced chemical vapor deposition (PECVD), and a 19-µm-width CBL pattern was defined by using standard photolithography and wet etching process; (f) a 100-nm-thick indium tin oxide (ITO) layer was then deposited on the p-GaN layer as current spreading layer by using an electronic beam evaporator; (g) a Cr/Pt/Au multi-layer films were deposited onto the exposed n-GaN layer and the ITO layer to serve as the n-electrode and p-electrode, respectively; (h)

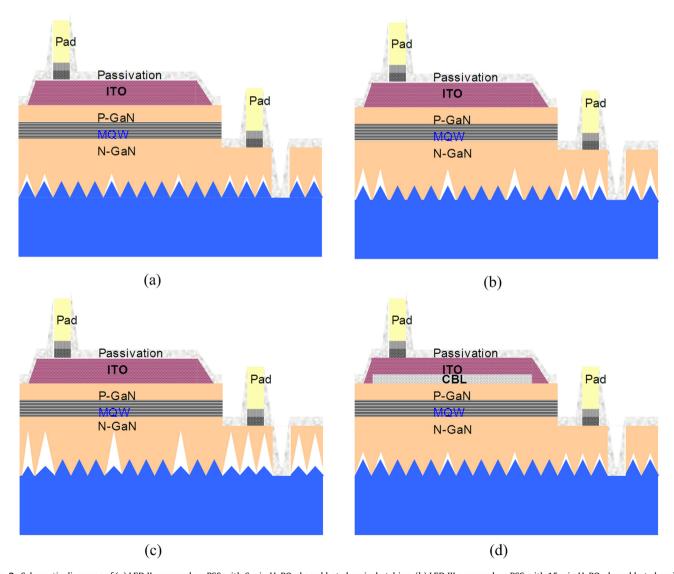

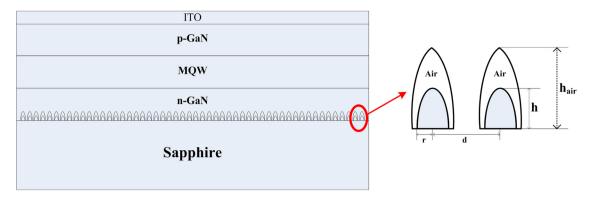

Fig. 2. Schematic diagrams of (a) LED II prepared on PSS with 6 min  $H_3PO_4$ -based hot chemical etching, (b) LED III prepared on PSS with 15 min  $H_3PO_4$ -based hot chemical etching, and (d) LED V prepared on PSS with 6 min  $H_3PO_4$ -based hot chemical etching and SiO<sub>2</sub> CBL.

A 69-nm-thick  $SiO_2$  passivation layer was deposited on the LED surface by PECVD. Finally, LED wafers were thinned to about 150  $\mu$ m by using backside lapping and polishing and broken into chips with size of 45 mil  $\times$  45 mil.

For comparison, the conventional LED grown on PSS (LED I) without air voids structure and CBL was prepared, and the LED V with air voids structure and SiO<sub>2</sub> CBL was also prepared. The schematic diagrams of the LED II, LED III, LED IV, and LED V were shown in Fig. 2. The LED II, LED III, and LED IV have different height of air void structure. The LED V and LED II have the same height of air void structure. Unlike the LED II, the LED V consists of not just air void structure, but rather of SiO<sub>2</sub> CBL. The scanning electron microscopy (SEM) and transmission electron microscopy (TEM) were used to evaluate cross-sectional profile of LED samples. Current–voltage (I-V) characteristics of LEDs were measured by a probe station system. Light output power of LEDs was measured by using an integrating sphere.

#### 3. Results and discussion

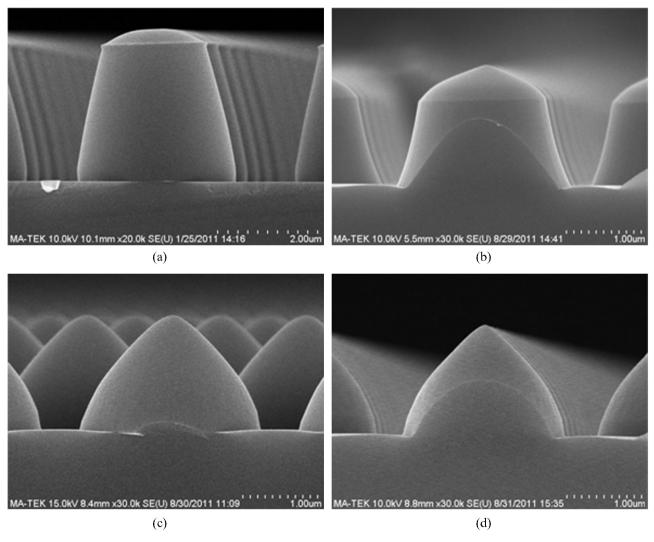

The PSS was fabricated by combining a thermally reflowed photoresist technique and an inductively coupled plasma (ICP) etching method [11]. First, a negative photoresist (NR71-3000P, Futurrex) of 4- $\mu$ m-thick was spin-coated on the c-plane (0001) flat sapphire

substrate. The photoresist was then patterned to be a circular shape by standard photolithography and reflowed during a hard baking process at  $125\,^{\circ}\text{C}$  to make a cone-shaped pattern. Subsequently, the sapphire substrate was etched by employing BCl<sub>3</sub>/Ar plasmas, and periodic cone-shaped patterns were formed on the sapphire substrate. During the ICP etching process, SEM images of sapphire at different etching time was shown in Fig. 3. Fig. 3(a) indicated that the sidewalls of patterns were almost vertical before the photoresist shrank. However, with the increasing etching time, the sidewalls, as shown in Fig. 3(b)–(d), were tapered as the photoresist shrank and the top surface of patterns was exposed to plasmas.

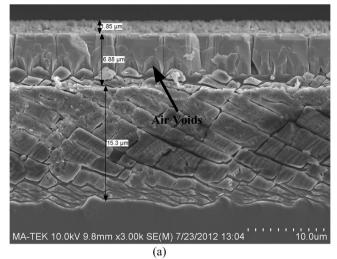

Fig. 4 showed the TEM image of LED epitaxial layer grown on the PSS with periodic cone shaped patterns (2.5  $\mu m$  diameter, 1.5  $\mu m$  height, and 0.5  $\mu m$  spacing). As shown in Fig. 4, it was found that the entire substrate was covered by GaN epitaxial layer. This is due to the use of cone shaped PSS which can significantly enhance the lateral growth of GaN. It was also noted that the threading dislocation density in the vicinity of GaN/PSS interface was higher than that away from the interface.

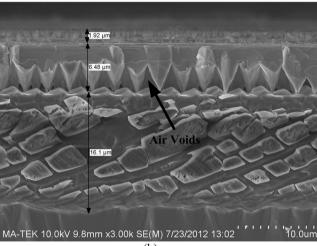

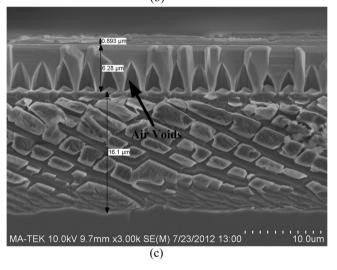

The cross-sectional SEM images of the LED II, LED III, LED IV were shown in Fig. 5. The inverted cone shaped air-void structure, as shown in Fig. 5, was formed between the PSS and GaN epitaxial layer after laser scribing and H<sub>3</sub>PO<sub>4</sub>-based hot chemical etching. The etching rate of GaN in the vicinity of GaN/PSS interface should

Fig. 3. SEM images of sapphire at different etching times: (a) 10 min, (b) 20 min, (c) 30 min, and (d) 35 min. Process condition: 1500 W/300 W of ICP/RF power, 7 mTorr of operating pressure, 50 sccm/10 sccm of BCl<sub>3</sub>/Ar flow rate.

Fig. 4. TEM image of the LED epitaxial layer grown on the PSS.

be much higher than that away from the interface because the threading dislocation density in the vicinity of GaN/PSS interface, as shown in Fig. 4, was higher than that away from the interface, especially the vicinity of GaN/PSS peak interface. Through defect-selective etching, the air voids structure was formed between the cone-shaped PSS and GaN epitaxial layer. As the wet etching time was increased from 6 min to 20 min, the average height of the air voids structure was 3  $\mu m$  (LED II), 4.5  $\mu m$  (LED III), and 4.8  $\mu m$  (LED IV), respectively. Meanwhile, the cone-shaped PSS was also etched, causing the reduction in the size of cone-shaped PSS, and the average height of cone-shaped PSS was 1.5  $\mu m$ , 0.7  $\mu m$ , and 0.5  $\mu m$ , respectively.

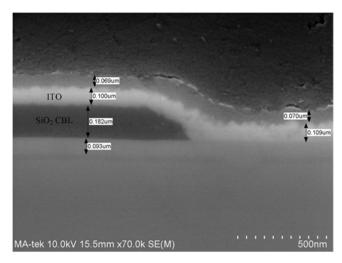

Fig. 6 showed the SEM image of the LED V with  $SiO_2$  CBL deposited beneath the p-electrode pad. A 182-nm-thick insulating  $SiO_2$  CBL underneath the 100-nm-thick ITO transparent conductive layer, as shown in Fig. 6, was used to deflect the current away from the p-electrode, resulting in better current spreading performance. A 69-nm-thick  $SiO_2$  passivation layer was deposited on the top of ITO transparent conductive layer, which can reduce the reverse leakage current and enhance the reliability of the high power LED chip.

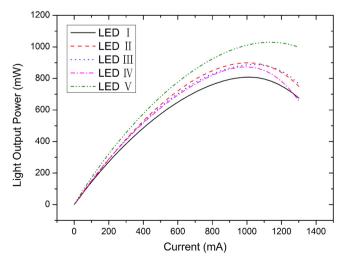

Fig. 7 showed the light output power of the fabricated five LEDs as a function of injection current. The measured light output power of LEDs by using an integrating sphere corresponds to the radiant power of electromagnetic radiation of a light source, and the unit of radiant power is the Watt [W]. Therefore, we used the unit (milli-Watt, mW) for the dimension of the vertical axis in Fig. 7. At 350 mA injection current, the light output powers of the five LEDs were 436 mW, 475 mW, 471 mW, 465 mW, 518 mW for the LED I, LED II, LED III, LED IV, and LED V, respectively. The light output power of the LED II was 8.9% higher than that of the LED I, which was primarily attributed to the increased light extraction through the top

Fig. 5. Cross-sectional SEM images of (a) LED II, (b) LED III, and (c) LED IV.

face due to a strong light reflection and redirection by the air voids [9]. Moreover, the light output power of LED II was slightly larger than that of LED III and LED IV. The light output power of LED V was 9.1% higher than that of LED II under 350 mA injection current. This enhancement was attributed to the improved current spreading performance and the increased current injection into the MQW active layer of the high power LED chip by employing SiO<sub>2</sub> CBL. The light output saturation current of LED I, LED II, LED III, LED IV, and

Fig. 6. SEM image of the LED V with SiO<sub>2</sub> CBL deposited beneath p-electrode pad.

LED V were 1021 mA, 1010 mA, 1021 mA, 1000 mA, and 1130 mA, respectively. The LED II and LED IV showed larger efficiency droop than other LEDs. The fluctuations of LED epitaxial structure may be the reason for the occurrence of this phenomenon. Additionally, the light output saturation current of LED V was significantly larger than other LEDs, which may be also attributed to the alleviated current crowding around *p*-electrode pad by the use of SiO<sub>2</sub> CBL, leading to the reduction in efficiency droop.

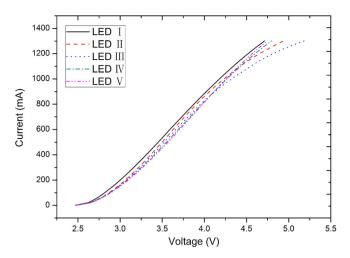

Fig. 8 showed the *I–V* (current–voltage) curves of the fabricated five LEDs. At 350 mA injection current, the forward voltages  $(V_f)$ of the fabricated five LEDs were 3.27 V, 3.32 V, 3.35 V, 3.36 V, and 3.39 V for LED I, LED II, LED III, LED IV, and LED V, respectively. The 350-mA-driven wall-plug efficiency of the fabricated five LEDs was 38.09%, 40.87%, 40.16%, 39.54%, 43.65% for the LED I, LED III, LED III, LED IV, and LED V, respectively, which was much higher than that of the reported LEDs with patterned sapphire and patterned ITO in the previous literature [4]. Compared to the conventional LED, a slightly increased  $V_f$  for the air voids embedded LEDs was observed, which could be attributed to the incomplete covering of the SiO<sub>2</sub> protection layer during the H<sub>3</sub>PO<sub>4</sub>-based hot chemical etching process, resulting in surface damage of p-GaN layer and thus higher serial resistances [12]. In contrast to the air voids embedded LED, a slightly increased  $V_f$  for the LED with SiO<sub>2</sub> CBL was also observed, which was attributed to the reduction in the total area of the p-type

Fig. 7. Light output power of LEDs with different structure.

Fig. 8. *I–V* characteristics of LEDs with different structure.

metal contact between the ITO layer and the p-GaN layer as a result of the presence of the insulating  $SiO_2$  layer.

To further investigate the principle of the LEE improvement by air voids structure, we used a ray tracing software (TracePro) to simulate light propagation in the LED chip. The LEE of the air voids embedded LEDs was calculated by using Monte Carlo ray-tracing method. The light absorption loss by the ITO and p-electrode was ignored to simplify the simulation process. Detailed parameters used in the simulation process were listed in Table 1. For the absorption models, different research groups have presented similar models such as  $0\,\mu\text{m}^{-1}$ ,  $1\,\mu\text{m}^{-1}$ ,  $0\,\mu\text{m}^{-1}$  [13],  $2\,\text{mm}^{-1}$ ,  $120\,\text{mm}^{-1}$ ,  $2\,\text{mm}^{-1}$ , 14], and  $5\,\text{mm}^{-1}$ ,  $8\,\text{mm}^{-1}$ ,  $5\,\text{mm}^{-1}$  [15]. In this simulation, the absorption coefficients of n-GaN, MQW, and p-GaN were assumed to be  $2\,\text{mm}^{-1}$ ,  $120\,\text{mm}^{-1}$ , and  $2\,\text{mm}^{-1}$ , respectively.

Fig. 9 showed the simulation structure used for the air voids embedded high power LED chip. The shape of the air void structure was assumed to be conical, which wrapped up the cone-shaped PSS. The dimensions of the PSS and air voids structure were determined from the SEM images shown in Fig. 5. The LED chip size, substrate thickness, and epitaxial layer thickness were  $1000 \, \mu m \times 1000 \, \mu m$ ,  $90 \, \mu m$ , and  $6.7 \, \mu m$ , respectively.

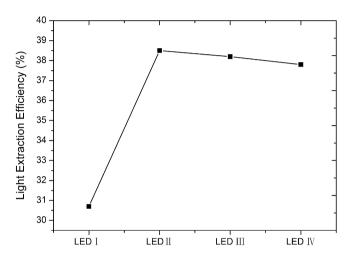

Fig. 10 showed the LEE of the air voids embedded LEDs simulated by using Monte Carlo ray-tracing method. In the simulation process, we used 600,000 light rays randomly emitted from the MQW active region layer of LED chip and collected by an integrating sphere. For each ray, the trajectory and the energy were determined by Snell's law, Fresnel losses and material absorption [13]. The LEE of the LED I, LED II, LED III, and LED IV were 30.7%, 38.5%, 38.2%, and 37.8%, respectively. It was found that the LEE of the air voids embedded high power LEDs (LED II, LED III, and LED IV) were all significantly larger than that of the PSS-LED (LED I). The LEE of the air voids embedded high power LED was decreased from 38.5% to 37.8% when the height of air voids structure was increased from 3  $\mu m$  to 4.8  $\mu m$ . The simulation results were in good agreement with the experimental results obtained from Fig. 7.

**Table 1**Detailed parameters used in the simulation process.

| Materials   | Refractive index  | Absorption coefficient |

|-------------|-------------------|------------------------|

| IVIALEITAIS | Refractive fildex | Absorption coefficient |

| Sapphire    | 1.78              | 0                      |

| n-GaN       | 2.42              | 2 mm <sup>-1</sup>     |

| MQW         | 2.54              | 120 mm <sup>-1</sup>   |

| p-GaN       | 2.45              | $2\mathrm{mm}^{-1}$    |

| ITO         | 1.95              | 0                      |

Fig. 9. Simulation structure for the air voids embedded high power LED.

Fig. 10. Simulated light extraction efficiency of LEDs by the TracePro software.

### 4. Conclusions

Air voids structure was embedded between PSS and GaN epitaxial layer by combining laser scribing with  $\rm H_3PO_4$ -based hot chemical etching to improve the LEE of the high power LED, and  $\rm SiO_2$  CBL underneath the p-electrode pad was utilized to improve the current spreading performance of the high power LED. The light

output power of the high power LED with embedded air void structure and  ${\rm SiO_2}$  CBL was 18% higher than that of the conventional PSS-LED.

#### Acknowledgement

This work was supported by the Project of the National Natural Science Foundation of China (No. 51305266).

#### References

- [1] P.C. Tsai, W.R. Chen, Y.K. Su, C.Y. Huang, Appl. Surf. Sci. 256 (2010) 6694.

- [2] M. Ma, J. Cho, E.F. Schubert, Y. Park, G.B. Kim, Appl. Phys. Lett. 101 (2012)

- [3] C.Y. Huang, H. Ku, S. Chao, Opt. Express 17 (2009) 23702.

- [4] S. Zhou, B. Cao, S. Liu, H. Ding, Opt. Laser Technol. 44 (2012) 2302.

- [5] C.C. Kao, Y.K. Su, C.L. Lin, IEEE Photonics Technol. Lett. 23 (2011) 986.

- [6] J.Y. Cho, K.J. Byeon, H. Lee, Opt. Lett. 36 (2011) 3203.

- [7] S. Zhou, S. Liu, Appl. Surf. Sci. 255 (2009) 9469.

- [8] Y.S. Zhao, D.L. Hibbard, H.P. Lee, K. Ma, W. So, H. Liu, J. Electron. Mater. 32 (2003) 1524.

- [9] E.H. Park, J. Jang, S. Gupta, I. Ferguson, C.H. Kim, S.K. Jeon, J.S. Park, Appl. Phys. Lett. 93 (2008) 191103.

- [10] S.C. Shei, H.M. Lo, W.C. Lai, W.C. Lin, S.J. Chang, IEEE Photonics Technol. Lett. 23 (2011) 1172.

- [11] S.H. Park, H. Jeon, Y.J. Sung, G.Y. Yeom, Appl. Opt. 40 (2001) 3698.

- [12] R.M. Lin, J.H. Li, J. Electrochem. Soc. 159 (2012) H433.

- [13] T.X. Lee, K.F. Gao, W.T. Chien, C.C. Sun, Opt. Express 15 (2007) 6670.

- [14] Z.Y. Liu, C. Li, B.H. Yu, Y.H. Wang, H.B. Niu, IEEE Photonics Technol. Lett. 24 (2012) 1558.

- [15] K. Wang, D. Wu, F. Chen, Z.Y. Liu, X.B. Luo, S. Liu, Opt. Lett. 35 (2010) 1860.